大きなリング共振器を解析する際の最適な方法

半径の大きなリング全体をFDTDなどでシミュレーションすると、計算量が膨大になることがあります。しかしながら、いくつか方法はあります。

varFDTD

Lumerical FDTDの代わりにLumerical MODEのvarFDTDソルバー(参照 )を用いるのが、このような大きなリングをシミュレーションするための一つの方法でしょう。

この2.5次元ソルバーは,2次元計算と同程度の計算負荷で3次元の平板構造を計算することができます。varFDTDを用いたリング共振器のシミュレーション例も用意されています。

この例を用いてシミュレーションを開始する前には、メモリの容量を確認してシミュレーションに必要な計算領域がPCに十分残されているかどうか確認してください。

また、このような大きなリングを解析するのにはシミュレーション時間を長くする必要があることにも注意が必要です。デフォルトの1000fsでは短いでしょう。

しかしながら、さらに大きなリング共振器をシミュレーションしたい場合は、varFDTDを用いるのは最適とはいえません。

Lumerical FDTD, Lumerical FDE, Lumerical INTERCONNECT

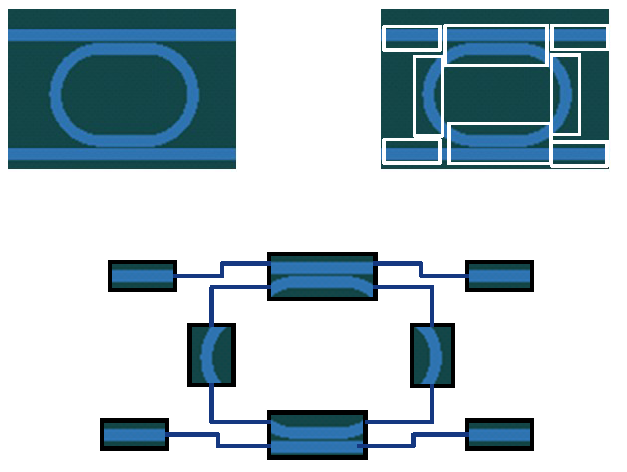

さらに大きなリング共振器を扱う場合、FDTDやvarFDTDでは事足りません。その場合、リング共振器デバイスをいくつかの要素に分けてシミュレーションを行い、得られたそれぞれのデータ

をLumerical INTERCONNECTにインポートしてシステムシミュレーションとして扱うのをお勧めします。

1- 結合部(Lumerical FDTD)

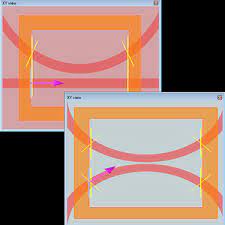

まず以下のスクリーンショットのように、リング部のシミュレーションを行います。これは、結合領域の散乱行列を得るためのシミュレーションです。

結合部(リング全体よりもずっと小さな領域)のみをシミュレーションしているので、FDTDで十分扱うことができるでしょう。FDTDで結合部が大きい場合は、varFDTDで初期パラメータをある程度最適化し、最終確認としてFDTD法を使用することを検討してもよいかもしれません。

2- 曲げ導波路(FDE)

FDEソルバーを用いて曲げ導波路をシミュレーションします。このシミュレーションでは、実行屈折率や郡屈折率さらには損失などの導波路特性を返すことができます。

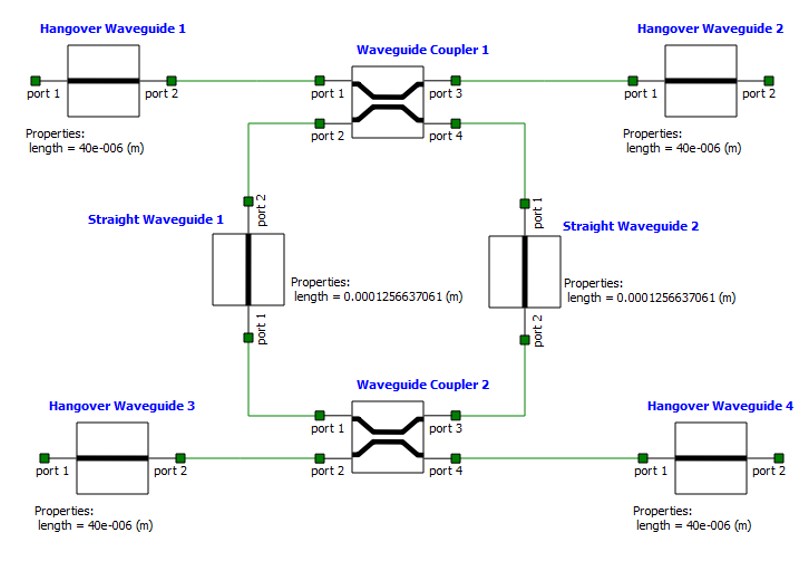

3- システムシミュレーション(Lumerical INTERCONNECT)

結合部の散乱行列と各要素の導波路特性が得られれば、それらをLumerical INTERCONNECTにインポートしてシステムシミュレーションを行うことができます。

このシミュレーションは正確であるだけでなく、Lumerical FDTDなどを用いてリング共振器全体を解析するより大幅に時間短縮が可能です(パッシブリングの例をご覧ください)。

リングが変調器である場合、関連する例があります。