PICシミュレーション用ランタイムライブラリとユーティリティ

Ansys社 Lumerical Photonic Verilog-A Platformは、業界をリードするEDAシミュレータと併用することで、マルチモード、マルチチャネル、双方向のフォトニック回路のモデリングを可能にし、エレクトロニック・フォトニック統合システムの設計と実装を促進します。

VERILOG-Aによるフォトニクスのモデリング

- 双方向性の光学ポート

- CML Compilerによるモデル生成でスケーラブルな光チャネルとモードを実現

- 光接続用の光バスがなく、回路図とレイアウトの整合性が保たれる

主な特徴

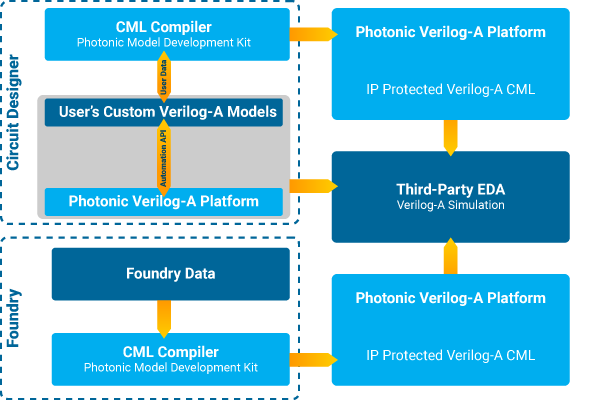

- CML Compilerによるバージョン管理されたモデルの自動生成と再現性の向上

- CML暗号化によるIP保護の提供

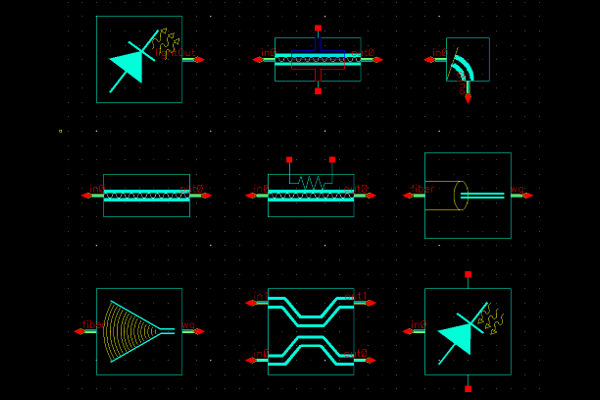

- CWレーザー、導波路、光位相シフター、光検出器、光NポートSパラメータ素子など、さまざまな固定モデルやパラメータ化されたフォトニックモデルが用意されています

カスタムモデルの作成

- CML CompilerによるVerilog-Aモデルの生成

- Lumerical社のVerilog-Aモデルをプロダクション・ファウンドリーのPDKから取得(近日公開予定)

- Lumerical社のVerilog-AランタイムAPIに基づいて、独自のカスタムVerilog-Aモデルを構築

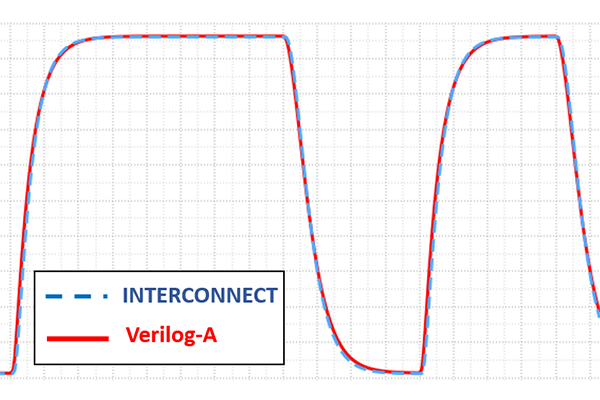

VERILOG-A VS. INTERCONNECT

- Lumerical社のVerilog-Aモデルは、コンポーネントの動作を正確に表現しており、CML Compilerを使用して同じデータソースから生成されたINTERCONNECTモデルとの一貫性があります。

- どちらのアプローチも、アプリケーションやシミュレーションの要件に応じて固有の利点があります。Verilog-Aモデルは、EDAシミュレータの多くの組み込み解析(例:AC解析、ノイズ解析)や高度な機能(例:可変タイムステッピング)を活用することができます。一方、INTERCONNECTはフォトニクス専用のクラス最高のシミュレータであり、双方向、マルチモード、マルチバンドのシミュレーションを自然に行うことができます。

- 設計の段階によって、どちらか一方、または両方のアプローチが必要になりますが、用途に応じて最適なものを選ぶことが成功の鍵です。